# МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РЕСПУБЛИКИ КАЗАХСТАН

# УНИВЕРСИТЕТ МИРАС

Игнашова Людмила Викторовна Жукова Татьяна Алексеевна

# АРХИТЕКТУРА КОМПЬЮТЕРНЫХ СИСТЕМ

Учебное пособие

УДК 004(075.8) ББК 32.973 я7 И26

Обсуждена и рассмотрена на Учебно-методическом совете (Протокол № 11 от 23.06.2017 года)

#### Рецензенты:

Тенизбаев Е.Ж. – к.т.н, доцент кафедры «Вычислительная техника и дизайн» ЮКГИ им. М. Сапарбаева

Джаманкараева М.А. – к.ф.-м.н, старший преподаватель кафедры «Вычислительная техника и дизайн» ЮКГИ им. М. Сапарбаева

Жукова Т.А. – к.т.н, доцент кафедры информационных технологий и телекоммуникаций университета «Мирас»

#### Игнашова Л.В., Жукова Т.А.

И26 **Архитектура компьютерных систем: учебное пособие.** – Шымкент, Университет «Мирас», 2017. - 186 с.

#### ISBN 978-9965-895-48-7

В учебном пособии в доступной форме представлены основные сведения о принципах функциональной и структурной организации вычислительных машин, систем, комплексов и сетей ЭВМ, арифметических, логических и схемотехнических основах ЭВМ; принципах организации внутренних и внешних запоминающих устройств; структуре процессоров; принципах работы устройств ввода и вывода информации и организации взаимодействия их с центральными устройствами; действиях с арифметикой двоичных чисел; основах проектирования вычислительных систем и сетей.

Книга предназначена для преподавателей ВУЗов и колледжей, а также для студентов, обучающихся по специальностям 5В060200 - «Информатика», 5В070400 - «Вычислительная техника и программное обеспечение», 5В070300 - «Информационные системы» в процессе изучения дисциплин «Архитектура компьютерных систем», «Организация и функционирование персонального компьютера», «Микропроцессорная техника».

УДК 004(075.8) ББК 32.973 я7

ISBN 978-9965-895-48-7

Игнашова Л.В., Жукова Т.А., 2017

# Содержание

| ВВЕДЕНИЕ                                                                                                                                                             | 4   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Тема 1. Основы организации ЭВМ                                                                                                                                       | 8   |

| Тема 2. Представление информации в ЭВМ. Арифметические и логические основы ЭВМ                                                                                       | 21  |

| Тема 3. Функциональные узлы ЭВМ                                                                                                                                      | 33  |

| Тема 4. Запоминающие устройства (ЗУ) ЭВМ                                                                                                                             | 47  |

| Тема 5. Оперативная память (RAM)                                                                                                                                     | 57  |

| Тема 6. Масочные, программируемые и репрограммируемые постоянные запоминающие устройства (ROM, PROM, EPROM, EPROM). Флэш-память. Память с последовательным доступом. |     |

| Видеопамять. Буферная память типа FIFO. Стековая память (LIFO)                                                                                                       | 73  |

| Тема 7. Процессоры ЭВМ                                                                                                                                               | 93  |

| Тема 8. Центральное устройство управления (ЦУУ)                                                                                                                      | 103 |

| Тема 9. Организация ввода - вывода. Вычислительные комплексы                                                                                                         | 123 |

| Тема 10. Интерфейсы передачи данных                                                                                                                                  | 130 |

| Тема 11. Распределенные системы обработки данных                                                                                                                     | 139 |

| Тема 12. Основы архитектуры персональных компьютеров                                                                                                                 | 154 |

| Тема 13. Структура микропроцессора                                                                                                                                   | 166 |

| СПИСОК ИСПОЛЬЗУЕМЫХ ИСТОЧНИКОВ                                                                                                                                       | 183 |

#### Введение

Целью изучения дисциплины «Архитектура компьютерных систем» является овладение:

- архитектурными особенностями современных ЭВМ и компьютерных систем;

- основами проектирования функциональных узлов и устройств ЭВМ;

- основами организации вычислительных комплексов.

В процессе изучения дисциплины студенты должны получить систематизированные знания об архитектуре компьютерных систем, организации и основных принципах работы устройств ЭВМ, в частности запоминающих устройств, процессоров и вычислительных комплексов в целом.

Основные задачи изучения дисциплины включают формирование у студентов знаний в следующих направлениях:

- -принципы функциональной и структурной организации вычислительных машин, систем, комплексов и сетей ЭВМ, арифметических, логических и схемотехнических основ ЭВМ;

- принципы организации внутренних и внешних ЗУ;

- структуру процессоров;

- -принципы работы устройств ввода и вывода информации и организация взаимодействия их с центральными устройствами;

- действий с арифметикой двоичных чисел;

- основы проектирования вычислительных систем и сетей.

- В процессе изучения дисциплины студенты должны получить систематизированные знания об архитектуре компьютерных систем, организации и основных принципах работы устройств ЭВМ, в частности запоминающих устройств, процессоров и вычислительных комплексов в целом.

Вычислительная техника прошла в своем развитии 4 стадии:

- компьютеры 1 поколения строились на электронных лампах;

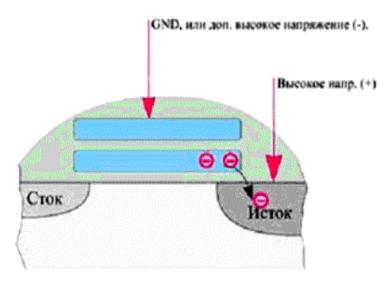

- компьютеры 2 поколения изготавливались с использованием транзисторов;

- компьютеры 3 поколения использовали интегральные микросхемы (интегральная схема это специальный кристалл кремния или германия, на котором сформированы участки со свойствами полупроводниковых электронных элементов (транзисторов, диодов, конденсаторов и т.п.; использование интегральных схем позволило существенно снизить размеры компьютеров, их стоимость и энергопотребление, увеличить быстродействие и объем памяти);

- компьютеры 4 и 5 поколений используют микропроцессор.

Первое поколение (1955-1960 гг.) строилось на дискретных элементах и вакуумных лампах, имели большие габариты, вес, мощность, обладая при этом малой надежностью. Они использовались в основном для решения научнотехнических задач атомной промышленности, реактивной авиации и ракетостроения.

Увеличению количества решаемых задач препятствовали низкая надежность и производительность, а также чрезвычайно трудоемкий процесс подготовки, ввода и отладки программы, написанной на языке машинных команд, т.е. в форме двоичных кодов.

Машины этого поколения имели быстродействие порядка 10-20 тысяч операций в секунду и ОП порядка 1К (1024 слова). В этот же период появились первые простые языки для автоматизированного программирования.

Второе поколение (1960-1965 гг.) использовали дискретные полупроводниковые приборы и миниатюрные дискретные детали, а в качестве технологической - печатный монтаж. По сравнению с предыдущим поколением резко уменьшились габариты и энергозатраты, возросла надежность. Возросли также быстродействие (приблизительно 500 тысяч оп/сек) и объем оперативной памяти (16-32К слов). Это сразу расширило круг пользователей, а, следовательно, и решаемых задач. Появились языки высокого уровня (Фортран, Алгол, Кобол) и соответствующие им трансляторы.

аппаратного Совершенствование обеспечения, построенного полупроводниковой базе, привело к тому, что появилась возможность строить в ЭВМ помимо центрального (основного) процессора еще ряд вспомогательных процессоров. Эти процессоры управляли всей периферией, в частности устройствами ввода/вывода, избавляли OT вспомогательной центральный процессор. Одновременно совершенствовались и ОС. Это позволило на ЭВМ второго поколения реализовать режим пакетной обработки также режим разделенного времени, необходимый параллельного решения нескольких задач управления производством. На машинах второго поколения были впервые опробованы ОП на ферритовых кольцах (так называемые кубы памяти). Все это позволило производство ЭВМ и привлечь к ней массу новых пользователей.

В ЭВМ *третьего поколения* (1965-1970 гг.) в качестве элементной базы использовались интегральные схемы малой интеграции с десятками активных элементов на кристалл, а также гибридные микросхемы из дискретных элементов. Это позволило сократить габариты и мощность, повысить быстродействие, снизить стоимость универсальных (больших) ЭВМ. Но самое главное - появилась возможность создания малогабаритных, надежных, дешевых машин - *мини*-ЭВМ.

Четвертое поколение (с 1970 г.). Успехи микроэлектроники позволили создать БИС и СБИС, содержащие десятки тысяч активных элементов. Это позволило разработать более дешевые ЭВМ с большой ОП. Стоимость одного байта памяти и одной машинной операции резко снизилась. Но затраты на программирование почти не сократились. Поэтому на первый план вышла задача экономии человеческих, а не машинных ресурсов.

Для этого разрабатывались новые ОС, позволяющие пользователю вести диалог с ЭВМ. Это облегчало работу пользователя и ускоряло разработку программ. Это потребовало, в свою очередь, организовать одновременный доступ к ЭВМ целого ряда пользователей, работающих с терминалов.

В 70-е же годы появились первые *микро-ЭВМ* - универсальные вычислительные системы, состоящие из процессора, памяти, схем сопряжения с устройствами ввода/вывода и тактового генератора, размещенные в одной БИС (*однокристальная* ЭВМ) или в нескольких БИС, установленных на одной печатной плате (*одноплатные* ЭВМ).

Совершенствование технологии позволило изготовить СБИС, содержащие сотни тысяч активных элементов, и сделать их достаточно дешевыми. Это привело к созданию небольшого настольного прибора, в котором размещалась микро-ЭВМ, клавиатура, экран, магнитный накопитель (кассетный или дисковый), а также схема сопряжения с малогабаритным печатающим устройством, измерительной аппаратурой, другими ЭВМ и т.д. Этот прибор получил название персональный компьютер.

В 1976г. была зарегистрирована компания Apple Comp (Стив Джекоб и Стефан Возняк), которая и начала выпуск первых в мире персональных компьютеров "Макинтош".

Благодаря ОС, обеспечивающей простоту общения с этой ЭВМ больших библиотечных прикладных программ, а также низкой стоимости, персональный компьютер начал стремительно внедрятся в различные сферы человеческой деятельности во всем мире. Об областях и целях его использования можно прочитать в многочисленных литературных источниках. По данным на 1985 год общий объем мирового производства уже составил  $200\cdot10^6$  микропроцессоров и  $10\cdot10^6$  персональных компьютеров в год.

Пятое поколение Характерной особенностью пятого поколения ЭВМ является то, что основные концепции этого поколения были заранее формулированы в явном виде. Задача разработки принципиально новых компьютеров впервые поставлена в 1979 году японскими специалистами, объединившими свои усилия под эгидой научно-исследовательского центра по обработке информации - JIPDEC. В 1981 г. JIPDEC опубликовал предварительный отчет, содержащий детальный план развертывания научно-исследовательских и опытно-конструкторских работ с целью создания к 1991 г. прототипа ЭВМ нового поколения.

В начале 70-х годов произошел технологический прорыв в области производства компьютерных компонентов - появились большие интегральные схемы. Их сравнительно невысокая стоимость и высокие функциональные возможности привели к созданию мини-компьютеров, которые стали реальными конкурентами мэйнфреймов. Закон Гроша перестал соответствовать действительности, так как десяток мини-компьютеров выполнял некоторые задачи (как правило, хорошо распараллеливаемые) быстрее одного мэйнфрейма, а стоимость такой мини-компьютерной системы была меньше.

Но шло время, потребности пользователей вычислительной техники росли, им стало недостаточно собственных компьютеров, им уже хотелось получить возможность обмена данными с другими близко расположенными компьютерами. В ответ на эту потребность предприятия и организации стали соединять свои мини-компьютеры вместе и разрабатывать программное обеспечение, необходимое для их взаимодействия. В результате появились

первые локальные вычислительные сети . Они еще во многом отличались от современных локальных сетей, в первую очередь - своими устройствами сопряжения. На первых порах для соединения компьютеров друг с другом использовались самые разнообразные нестандартные устройства со своим способом представления данных на линиях связи, своими типами кабелей и т. п. Эти устройства могли соединять только те типы компьютеров, для которых были разработаны.

В середине 80-х годов утвердились стандартные технологии объединения компьютеров в сеть - Ethernet, Arcnet, Token Ring. Мощным стимулом для их развития послужили персональные компьютеры. Эти массовые продукты явились идеальными элементами для построения сетей - с одной стороны, они были достаточно мощными для работы сетевого программного обеспечения, а с другой - явно нуждались в объединении своей вычислительной мощности для решения сложных задач, а также разделения дорогих периферийных устройств и дисковых массивов. Поэтому персональные компьютеры стали преобладать в локальных сетях, причем, не только в качестве клиентских компьютеров, но и в качестве центров хранения и обработки данных, то есть сетевых серверов, потеснив с этих привычных ролей мини-компьютеры и мэйнфреймы.

Стандартные сетевые технологии превратили процесс построения локальной сети из искусства в рутинную работу. Для создания сети достаточно было приобрести сетевые адаптеры соответствующего стандарта, например Ethernet, стандартный кабель, присоединить адаптеры к кабелю стандартными разъемами и установить на компьютер одну из популярных сетевых операционных систем, например, NetWare. После этого сеть начинала работать и присоединение каждого нового компьютера не вызывало никаких проблем - естественно, если на нем был установлен сетевой адаптер той же технологии.

Последствием и одновременно движущей силой такого прогресса стало появление огромного числа непрофессиональных пользователей, которым совершенно не нужно было изучать специальные (и достаточно сложные) команды для сетевой работы. А возможность реализовать все эти удобства разработчики локальных сетей получили в результате появления качественных кабельных линий связи, на которых даже сетевые адаптеры первого поколения обеспечивали скорость передачи данных до 10 Мбит/с.

## Контрольные вопросы:

- 1. Каковы цели и задачи изучения дисциплины?

- 2. Что изучает дисциплина?

- 3. Какие базовые знания нужны для изучения дисциплины?

- 4. Почему необходимо изучать курс «Архитектура компьютерных систем» студентам специальности «Информационные системы»?

- 5. Каковы современные тенденции развития средств вычислительной техники?

- 6. Этапы развития ВК, ВС и сетей.

#### Тема 1. Основы организации ЭВМ

- 1. Состав и назначение элементов компьютерных систем.

- 2. Классификация ЭВМ.

- 3. Основные устройства ЭВМ и их назначение. Архитектура, структура и интерфейсы ЭВМ.

- 4. Принцип программного управления работой ЭВМ.

- 5. Основные характеристики и параметры ЭВМ.

#### 1 Состав и назначение элементов компьютерных систем.

Электронные вычислительные машины (ЭВМ) являются преобразователями информации. В них исходные данные задачи преобразуются в результат ее решения. В соответствии с используемой формой представления информации машин делятся на два больших класса - *аналоговые* и дискретного действия - *цифровые*. Их обозначают как АВМ и ЦВМ. В настоящее время термин ЭВМ относят именно к машине дискретного действия или ЦВМ, принципы, функционирования которых и будут рассмотрены в настоящем курсе.

Компьютер (ЭВМ) - это техническое устройство, предназначенное для обработки больших объёмов информации.

Под техническим устройством подразумевается объект искусственного происхождения, изготовленный специально с вполне определённым функциональным назначением.

Информацией называется совокупность данных произвольной природы, которые несут для пользователя вполне определённые сведения.

Данными называются материальные объекты, обладающие свойством отображать и нести на себе информацию. Их основное назначение заключается в том, чтобы материализовать информацию.

Обработка информации — её целенаправленное преобразования, то есть такое воздействие на информацию, которое оставляет различимые следы её преобразования. Автоматическая обработка информации характеризуется тем, что она выполняется в полном объеме без какого-либо участия человека.

Основные характеристики ЭВМ определяются характеристиками его компонентов. Каждый компонент представляет собой отдельное устройство, которое может как само по себе, так может и во взаимодействии с другими устройствами и определяет характеристики ЭВМ.

К основным компонентам ЭВМ относятся: центральный процессор, системная плата, основная память, монитор, жесткий диск, графическая карта, дисковод для компакт-дисков.

## 2 Классификация ЭВМ

Любая сфера человеческой деятельности, любой процесс функционирования технического объекта связаны с передачей и

преобразованием информации. Одно из важнейших положений кибернетики состоит в том, что без информации, ее передачи и переработки невозможны организованные системы — ни биологические, ни технические, искусственно созданные человеком.

В общем случае сообщения могут быть непрерывными (аналоговыми) и дискретными (цифровыми).

Аналоговое сообщение представляется некоторой физической величиной (обычно электрическим током или напряжением), изменение которой во времени отражает протекание рассматриваемого процесса, например температуры в нагревательной печи. Физический процесс, передающий непрерывное сообщение, может в определенном интервале принимать любые значения и изменяться в произвольные моменты времени, т.е. может иметь бесконечное множество состояний.

Дискретное сообщение характеризуется конечным набором состояний, например, передача текста. Каждое из этих состояний можно представить в виде конечной последовательности символов или букв, принадлежащих конечному множеству, называемому алфавитом. Такая операция называется кодированием, а последовательность символов — кодом. Число символов, входящих в алфавит, называется основанием кода. Важным здесь является не физическая природа символов кода, а то, что за конечное время можно передать только конечное число состояний сообщения. Причем, чем меньше основание кода, тем длиннее требуются кодовые группы для передачи фиксированного набора состояний сообщения.

В настоящее время в абсолютном большинстве случаев используются коды с основанием два, т.е. информация представляется в виде бинарных импульсных последовательностей, или двоичных кодов.

Передачу и преобразование любой дискретной информации всегда можно свести к эквивалентной передаче и преобразованию двоичных кодов, или иифровой информации.

Более того, возможно с любой заранее заданной степенью точности непрерывное сообщение заменить цифровым путем квантования непрерывного сообщения по уровню и дискретизации его по времени. Однако следует иметь в виду, что с увеличением точности представления аналогового сообщения растет разрядность кода. Это может привести к тому, что обработка аналогового сообщения в цифровой форме на конкретной ЭВМ в реальном масштабе времени окажется невозможной.

Таким образом, *любое* сообщение может быть с определенной степенью точности представлено в *цифровой* форме.

Электронные вычислительные машины (ЭВМ) являются преобразователями информации. В них исходные данные задачи преобразуются в результат ее решения. В соответствии с используемой формой представления информации при преобразовании ЭВМ делятся на два больших класса — аналоговые и дискретного действия — цифровые. Их обозначают как АВМ и ЦВМ соответственно. С 70-х годов термин ЭВМ относят именно к машинам

дискретного действия, или ЦВМ, принципы функционирования которых и будут рассмотрены в настоящем курсе.

# 3 Основные устройства ЭВМ и их назначение. Архитектура, структура и интерфейсы ЭВМ

Как уже отмечалось, современная ЭВМ есть вычислительный автомат, который представляет собой техническое устройство, способное автоматически исполнять заданные вычислительные алгоритмы. Данное назначение ЭВМ определяет её функциональную структуру и принцип действия.

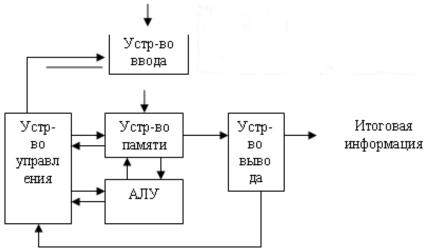

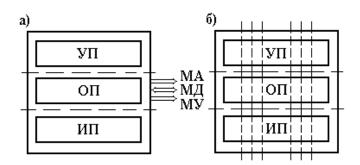

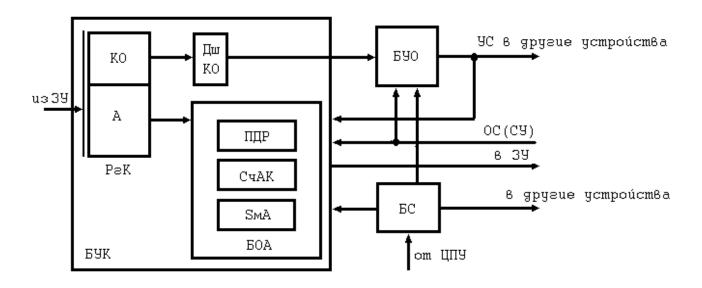

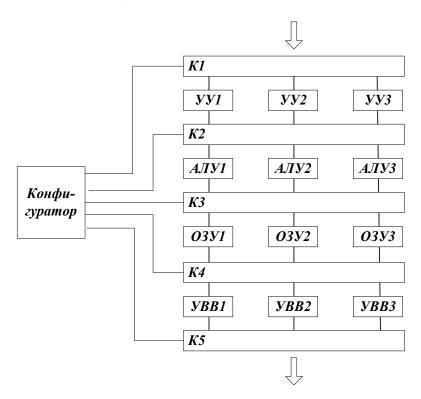

Структурой какого-либо объекта принято называть его поэлементный состав с учётом существующих взаимосвязей между элементами. Рассмотрим функциональную структуру ЭВМ на уровне типовых укрупнённых функциональных блоков, то есть таких элементов конструкций, которые представляют собой основные самостоятельные устройства в составе ЭВМ (рисунок 1).

Рисунок 1 – Структура ЭВМ

Центральным устройством ЭВМ является устройство памяти (УП). Оно выполняет функцию накопления и хранения данных в процессе их обработки. Различают 2 вида памяти:

- А) Основная память;

- Б) Вспомогательная память.

Основная память включает следующие компоненты:

- 1) Оперативное запоминающее устройство (ОЗУ)

- 2) Постоянное запоминающее устройство (ПЗУ)

- 3) Программируемое (переменное) запоминающее устройство (ППЗУ)

- 4) Регистры

- 5) Аккумуляторы

Главным элементом основной памяти является ОЗУ. Оно выполняет функцию накопления и хранения данных оперативного доступа. Доступом называется произвольная операция обращения к памяти. Данные оперативного

доступа характеризуются тем, что могут изменять свои значения по ходу вычислительного процесса произвольное число раз. При этом требуют максимально возможной скорости обработки.

ОЗУ представляет собой основное рабочее место ЭВМ. При этом оно характеризуется тем, что имеет постоянный ограниченный объём, и этот объём в первую очередь определяет вычислительную производительность ЭВМ. ОЗУ обеспечивает самый короткий доступ к хранимым данным. Масштаб времени доступа составляет доли микросекунд.

ПЗУ представляет собой такой элемент памяти, в котором хранимая информация организована и представлена как элемент конструкции. Т. о. Данная информация является постоянной характеристикой устройства и не допускает своего изменения без вмешательства в конструкции, т.е. без разрушения самого устройства. ПЗУ выполняется в виде самостоятельной съёмной детали в структуре ЭВМ.

ППЗУ - такое ПЗУ, в котором существует возможность внесения изменений в хранимую информацию (перепрограммирование). Такое перепрограммирование выполняется с помощью специализированных устройств, называемых программаторами. Устройство типа ППЗУ ещё называют элементами флэш-памяти.

Регистром называется элемент рассредоточенной памяти ёмкостью, соизмеримой с размером одного цифрового машинного слова. Обычно регистры выполняют функцию «персонального обслуживания» устройства, за которым он закреплён. В современных моделях ЭВМ регистры образуют внутреннюю индивидуальную память микропроцессора.

Аккумулятором называется специализированный регистр, предназначенный для прямого обслуживания АЛУ.

Вспомогательная (внешняя) память выполняет функцию накопления и хранения информации архивного назначения. Архивная информация характеризуется тем, что:

- 1) Предназначается для длительного хранения, т.е. для хранения такой промежуток времени, который превосходит длительность одного отдельно взятого вычислительного процесса.

- 2) Данные в составе архивной информации ориентированы на использование не в одной отдельно взятой задаче, а в различных задачах.

- 3) Архивные данные допускают обращение к ним произвольное количество раз, причём из различных задач. При этом обращение к данным не допускает никакого изменения этих данных. Т.е. к таким данным разрешено обращение только на чтение.

- 4) Архивная информация предполагает достаточно большой объём, т.е. такой объём, который покрывает все возникающие потребности. Отсюда следует, что размер внешней памяти для хранения архива должен быть практически ничем не ограничен.

Внешняя память конструктивно выполняется в виде накопителей информации. Такие накопители характеризуются тем, что обеспечивают

возможность закрепления (записи) информации на специальных машинных носителях.

Для измерения ёмкости памяти ЭВМ используются специальные единицы, основной из которой является 1 байт. 1 байт — это такое место в памяти ЭВМ, куда может быть размещён 1 элементарный символ информации. Такой символ не может быть разделён на составляющие без потери признаков символа.

Для современных ЭВМ со средними показателями вычислительной производительности характерны следующие показатели ёмкости памяти:

Ёмкость ОЗУ -128-256 MB

Ёмкость винчестера – 1ГВ

Ёмкость стандартного гибкого диска с определяющим размером 3,5 дюйма – 1,44 MB.

Ёмкость регистра памяти соизмеряется с длиной 1 цифрового машинного слова, т.е. цифровой комбинации, заданной стандартной длиной в байтах.

Арифметико-логическое устройство. АЛУ выполняет функцию воспроизведения заданной элементарной вычислительной операции над заданными данными.

Вычислительной операцией называется некое вычислительное действие над данными. Всякая операция, предназначенная для исполнения на ЭВМ, должна быть предварительно описана в форме записи. Запись операции характеризуется тем, что представляет собой совокупность некоторого числа данных, соединённых символами вычислительных операций. Операции по масштабу делятся на составные и элементарные. Составные операции характеризуются тем, что они всегда могут быть разбиты на отдельные элементарные операции, тогда как элементарные операции не могут быть разбиты на составляющие без потери признаков операции.

Устройство управления (УУ). УУ выполняет функцию обеспечения совместной согласованной работы всех устройств ЭВМ.

В современных ЭВМ АЛУ и УУ конструктивно объединены в одном функциональном блоке, который называется процессором. Такой процессор, выполненный по микроэлектронной технологии, называется микропроцессором. Т.о процессор в ЭВМ представляет собой собственно автоматическое вычислительное устройство. Его технические характеристики определяют вычислительную производительность ЭВМ. Основными такими характеристиками являются показатели разрядности и тактовой частоты.

Разрядностью процессора называется количество информации, которое способен обработать процессор единовременно за 1 акт (т.е. за 1 движение). Тактовая частота - это количество тактов, которое вырабатывает устройство отсчёта времени ЭВМ (следовательно, микропроцессора) в 1 физическую секунду. 1 такт - это минимальная порция времени, различаемая устройствами ЭВМ. Тактовая частота измеряется в Гц. 1 Гц =1 такт/сек. На практике пользуются производной единицей 1 МГц-106 такт/сек.

Т.о., показатель разрядности определяет порцию единовременно обрабатываемой информации, а тактовая частота определяет скоростные

характеристики микропроцессора и ЭВМ в целом. Показатель разрядности оценивается числом двоичных разрядов (числом бит).

Устройство ввода выполняет функцию загрузки памяти ЭВМ (ОЗУ) исходной информации для счёта. Исходной информацией считается такая, которая должна быть задана и определена на момент начала вычислительного процесса, т.к. без этого вычислительный процесс не может начаться. Функция ввода организуется на основе автоматического преобразования информации представления домашинной формы В информацию внутримашинного представления с последующим размещением преобразованной информации в современных ЭВМ в качестве стандартных устройств ввода используюся клавиатура и накопители внешней памяти в режиме чтения. Стандартные устройства- это такие устройства, которые входят в обязательный комплект поставки ЭВМ.

Устройство вывода (УВ) выполняет функцию выгрузки из памяти ЭВМ, отображения их в соответствии с требованиями и при необходимости закрепления (записи) на технический носитель для цели длительного хранения. Эта функция выполняется на основе преобразования информации внутримашинной формы представления во внемашинную форму.

Магистрально-модульный принцип организации ЭВМ получил широкое распространение, поскольку в этом случае все устройства используют единый подход сопряжения модулей центральных процессоров и устройств ввода/вывода с помощью стандартных шин.

Традиционно шины делятся на шины, обеспечивающие организацию связи процессора с памятью, и шины ввода/вывода. Шины ввода/вывода могут иметь большую протяженность, поддерживать подсоединение многих типов устройств и обычно следуют одному из шинных стандартов. Шины процессорпамять, с другой стороны, сравнительно короткие, обычно высокоскоростные и соответствуют организации системы памяти для обеспечения максимальной пропускной способности канала память-процессор. На этапе разработки системы для шины процессор-память заранее известны все типы и параметры устройств, которые должны соединяться между собой, в то время как разработчик шины ввода/вывода должен иметь дело с устройствами, различающимися по задержке и пропускной способности.

С целью снижения стоимости некоторые компьютеры снабжаются единственной шиной для памяти и устройств ввода/вывода. Такая шина часто называется системной. Персональные компьютеры, как правило, строятся на основе одной системной шины.

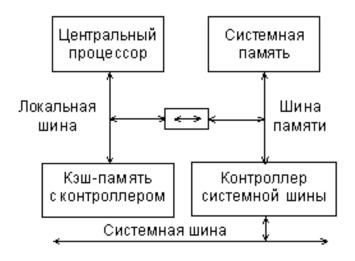

Необходимость сохранения баланса производительности по мере роста быстродействия микропроцессоров привела к двухуровневой организации шин в персональных компьютерах на основе локальной шины.

Локальной шиной называется шина, выходящая непосредственно на контакты микропроцессора. Она обычно объединяет процессор, память, схемы буферизации для системной шины и ее контроллер, а также некоторые вспомогательные схемы. Типичными примерами локальных шин являются VL-Bus и PCI.

На современных компьютерах часто используется специальная магистраль обмена данными с процессором — локальная видеошина. AGP (Accelerated Graphics Port - ускоренный графический порт) — скоростная шина для связи с графической картой. Разработана Intel для высокоскоростной графики. Основное преимущество этой шины заключается в скорости.

Различают шины синхронные и асинхронные. Синхронная шина использует сигналы синхронизации, которые передаются по линиям управления шины, и фиксированный протокол, определяющий расположение сигналов адреса и данных относительно сигналов синхронизации. Эти шины являются и быстрыми, и дешевыми. Однако они имеют два главных недостатка. Все на шине должно происходить с одной и той же частотой синхронизации, поэтому из-за проблемы перекоса синхросигналов синхронные шины не могут быть длинными. Обычно такие шины связывают процессор и память.

Асинхронная шина не тактируется. Вместо этого обычно используется старт-стопный режим передачи и протокол «рукопожатия» (handshaking) между источником и приемником данных на шине. Эта схема позволяет гораздо проще приспособить широкое разнообразие устройств и удлинить шину без беспокойства о перекосе сигналов синхронизации и о системе синхронизации. Асинхронные шины по мере изменения технологии лучше масштабируются. Они обычно используются в устройствах ввода/вывода.

Стандарты шин. Обычно количество и типы устройств ввода/вывода в вычислительных системах не фиксируются, что позволяет пользователю самому подобрать необходимую конфигурацию. Шина ввода/вывода компьютера может рассматриваться как шина расширения, обеспечивающая постепенное наращивание устройств ввода/вывода. Поэтому стандарты играют огромную роль, позволяя разработчикам компьютеров и устройств ввода/вывода работать независимо. Появление стандартов определяется разными обстоятельствами.

Иногда широкое распространение и популярность конкретных машин становятся причиной того, что их шина ввода/вывода становится стандартом де-факто. Примерами таких шин могут служить PDP-11 Unibus и IBM PC/AT Bus. Иногда стандарты появляются также в результате определенных достижений по стандартизации в некотором секторе рынка устройств ввода/вывода. Интеллектуальный периферийный интерфейс (IPI - Intelligent Peripheral Interface) и Ethernet являются примерами стандартов, появившихся в результате кооперации производителей. Успех того или иного стандарта в значительной степени определяется его принятием такими организациями как ANSI (Национальный институт по стандартизации США) или IEEE (Институт инженеров по электротехнике и радиоэлектронике). Иногда стандарт шины может быть прямо разработан одним из комитетов по стандартизации: примером такого стандарта шины является FutureBus.

Одной из популярных шин персональных компьютеров была системная шина *IBM PC/XT*, обеспечивавшая передачу 8 бит данных. Кроме того, эта шина включала 20 адресных линий, которые ограничивали адресное пространство пределом в 1 Мбайт. Для работы с внешними устройствами в этой шине были предусмотрены также 4 линии аппаратных прерываний (IRQ) и

4 линии для требования внешними устройствами прямого доступа к памяти (DMA). Для подключения плат расширения использовались специальные 62-контактные разъемы. При этом системная шина и микропроцессор синхронизировались от одного тактового генератора с частотой 4.77 МГц. Таким образом, теоретическая скорость передачи данных могла достигать немногим более 4 Мбайт/с.

Системная шина *ISA* (Industry Standard Architecture) впервые стала применяться в персональных компьютерах IBM PC/AT на базе процессора 80286. Для этой системной шины характерно наличие второго, 36-контактного дополнительного разъема для соответствующих плат расширения. За счет этого количество адресных линий было увеличено на 4, а данных - на 8, что позволило передавать параллельно 16 бит данных и обращаться к 16 Мбайт системной памяти. Количество линий аппаратных прерываний в этой шине было увеличено до 15, а каналов прямого доступа - до 7. Системная шина ISA полностью включала в себя возможности старой 8-разрядной шины. Шина ISA позволяет синхронизировать работу процессора и шины с разными тактовыми частотами. Она работает на частоте 8 МГц, что соответствует максимальной скорости передачи 16 Мбайт/с.

С появлением процессоров 80386, 80486 и Pentium шина ISA стала узким местом персональных компьютеров на их основе. Новая системная шина EISA (Extended Industry Standard Architecture), появившаяся в конце 1988 года, обеспечивает адресное пространство в 4 Гбайта, 32-битовую передачу данных (в том числе и в режиме DMA), улучшенную систему прерываний и арбитраж DMA, автоматическую конфигурацию системы и плат расширения. Устройства шины ISA могут работать на шине EISA. Шина EISA предусматривает централизованное управление доступом к шине за счет наличия специального устройства - арбитра шины. Поэтому к ней может подключаться несколько главных устройств шины. Улучшенная система прерываний позволяет подключать к каждой физической линии запроса на прерывание несколько устройств, что снимает проблему количества линий прерывания. Шина EISA тактируется частотой около 8 МГц и имеет максимальную теоретическую скорость передачи данных 33 Мбайт/с.

Шина *MCA* также обеспечивает 32-разрядную передачу данных, тактируется частотой 10 МГц, имеет средства автоматического конфигурирования и арбитража запросов. В отличие от EISA она не совместима с шиной ISA и используется только в компьютерах компании IBM.

Шина *VL-bus*, предложенная ассоциацией VESA (Video Electronics Standard Association), предназначалась для увеличения быстродействия видеоадаптеров и контроллеров дисковых накопителей для того, чтобы они могли работать с тактовой частотой до 40 МГц. Шина VL-bus имеет 32 линии данных и позволяет подключать до трех периферийных устройств, в качестве которых наряду с видеоадаптерами и дисковыми контроллерами могут выступать и сетевые адаптеры. Максимальная скорость передачи данных по шине VL-bus может составлять около 130 Мбайт/с.

Шина PCI (Peripheral Component Interconnect) также, как и шина VL-bus, поддерживает 32-битовый канал передачи данных между процессором и периферийными устройствами, работает на тактовой частоте 33 МГц и имеет 120 максимальную пропускную способность Мбайт/с. При процессорами 80486 шина PCI примерно дает те же показатели производительности, что и шина VL-bus. Однако, в отличие от последней, шина PCI процессорно независимой (шина VL-bus является подключается непосредственно к процессору 80486 и только к нему). Ее легко подключить к различным центральным процессорам. В их числе Pentium, Alpha, R4400 и PowerPC.

Основные возможности шины РСІ:

- синхронный протокол обмена, предусматривающий подтверждение о приеме, что позволяет пересылать данные со скоростью, максимально возможной для приемного устройства (в отличие от ISA);

- в РС используется 32-разрядная шина РСІ с частотой 33 МГц. Однако шина РСІ процессорно независимая, и спецификация допускает ширину в 64 разряда и частоту 66 МГц. Это используется, например, в компьютерах компании Sun, в серверах на базе ЦП Alpha и Intel Xeon. Слот 32-разрядной шины РСІ имеет 124 контакта (у 64-разрядной есть еще дополнительная секция);

- вставляемые платы автоматически конфигурируются (при старте) по стандарту Plug and Play, т.е. не надо вручную устанавливать перемычки и переключатели, чтобы избежать конфликтов с другими устройствами;

- для пользователя шина предоставляет слоты (не более пяти). Это так называемый сегмент PCI;

- спецификация PCI допускает произвольное число сегментов, образующих древовидную топологию. Для соединения сегментов используются PCI-мосты;

- есть режим Bits mastering, дающий устройству возможность брать управление шиной на себя и тем самым разгрузить ЦП;

- начиная с версии 2.2 (внедрена в 1999 г.) в шину включена линия, управляющая пробуждением компьютера от PCI-устройства, например, модема, сетевой карты.

PCI Special Interest Group в октябре 1999 г. объявила о выходе спецификации PCI-X 1.0. Спецификация представляет собой окончательный вариант преемницы PCI-шины. Основным достоинством новой шины является увеличенная до 133 МГц частота при сохранившейся обратной совместимости с PCI-картами.

Одной из популярных шин ввода-вывода является шина SCSI. Под термином SCSI - Small Computer System Interface (Интерфейс малых вычислительных систем) обычно понимается набор стандартов, разработанных Национальным институтом стандартов США (ANSI) и определяющих механизм реализации магистрали передачи данных между системной шиной компьютера и периферийными устройствами.

Первоначально SCSI предназначался для использования в небольших дешевых системах и поэтому был ориентирован на достижение хороших результатов при низкой стоимости. Характерной его чертой является простота, особенно в части обеспечения гибкости конфигурирования периферийных устройств без изменения организации основного процессора. Главной особенностью подсистемы SCSI является размещение в периферийном оборудовании интеллектуального контроллера.

Для достижения требуемого высокого уровня независимости от типов периферийных устройств в операционной системе основной машины, устройства SCSI представляются имеющими очень простую архитектуру. Например, геометрия дискового накопителя представляется в виде линейной последовательности одинаковых блоков, хотя в действительности любой диск имеет более сложную многомерную геометрию, содержащую поверхности, цилиндры, дорожки, характеристики плотности, таблицу дефектных блоков и множество других деталей. В этом случае само устройство или его контроллер несут ответственность за преобразование упрощенной SCSI модели в данные для реального устройства.

Начальный стандарт 1986 года, известный теперь под названием SCSI-1, определял рабочие спецификации протокола шины, набор команд и электрические параметры. Шина данных SCSI-1 использовала 50-жильный экранированный кабель, имела разрядность 8 бит, а максимальная скорость передачи составляла 5 Мбайт/сек.

В 1992 году этот стандарт был пересмотрен с целью устранения недостатков первоначальной спецификации (особенно в части синхронного режима передачи данных) и добавления новых возможностей повышения производительности, таких как «быстрый режим» (fast mode), «широкий режим» (wide mode) и помеченные очереди. Этот пересмотренный стандарт получил название SCSI-2 и в настоящее время используется большинством поставщиков вычислительных систем.

Стандарт SCSI-2 определяет, в частности, различные режимы: Wide SCSI, Fast SCSI и Fast-and-Wide SCSI. Fast SCSI сохраняет 8-битовую шину данных и поэтому может использовать те же самые физические кабели, что и SCSI-1. Он отличается только тем, что допускает передачи со скоростью 10 Мбайт/сек в синхронном режиме. Wide SCSI удваивает либо учетверяет разрядность шины данных (либо 16, либо 32 бит), допуская соответственно передачи со скоростью либо 10, либо 20 Мбайт/сек. В комбинации Fast-and-Wide SCSI возможно достижение скоростей передачи 20 и 40 Мбайт/сек соответственно.

Однако поскольку в обычном 50-жильном кабеле просто не хватает жил, комитет SCSI решил расширить спецификацию вторым 66-жильным кабелем (так называемый В-кабель). В-кабель имеет дополнительные линии данных и ряд других сигнальных линий, позволяющие реализовать режим Fast-and-Wide.

В реализации режима Wide SCSI предложена также расширенная адресация, допускающая подсоединение к шине до 16 устройств (вместо стандартных восьми). Это значительно увеличивает гибкость подсистемы SCSI,

правда, приводит к появлению дополнительных проблем, связанных с эффективностью ее использования.

Реализация режимов Wide-SCSI и Fast-and-Wide SCSI до 1994 года редко использовалась, поскольку эффективность их применения не была достаточно высокой. Однако широкое распространение дисковых массивов и дисковых накопителей со скоростью вращения 7200 оборотов в минуту делают эту технологию весьма актуальной.

#### 4 Принцип программного управления работой ЭВМ

Для того, чтобы понять принцип программного управления ЭВМ, необходимо определить понятия *алгоритм* и *программа*. Понятие алгоритма не замыкается только областью вычислительной техники (ВТ). По интуитивному определению:

Aлгоритм — это совокупность правил, строго следуя которым можно перейти от исходных данных к конечному результату.

В вычислительной технике под "совокупностью правил" понимается последовательность арифметических и логических операций. (Утверждают, что слово *алгоритм* произошло от имени Мухаммед аль Хорезми, написавшем в IX веке трактат по арифметике десятичных чисел.)

Программа — это запись алгоритма в форме, воспринимаемой ЭВМ. Любая программа состоит из отдельных команд. Каждая команда предписывает определенное действие и указывает, над какими операндами это действие производится. Программа представляет собой совокупность команд, записанных в определенной последовательности, обеспечивающих решение задачи на ЭВМ. Для того, чтобы УУ могло воспринять команды, они должны быть закодированы в цифровой форме (во всех современных ЭВМ — это двоичный код).

Автоматическое управление процессом решения задачи достигается на основе *принципа программного управления*, являющегося основной особенностью ЭВМ. (Без программного управления ЭВМ превратится в обычный быстродействующий арифмометр или калькулятор.).

Другим важнейшим принципом является *принцип хранимой в памяти программы*. Согласно этому принципу программа, закодированная в цифровом виде, хранится в памяти наравне с числами. Поскольку программа хранится в памяти, одни и те же команды можно извлекать и выполнять необходимое количество раз. Более того, над кодами команд можно выполнять некоторые арифметические операции и тем самым *модифицировать* адреса обращения к ОП.

Команды программы выполняются в порядке, соответствующем их последовательных ячейках Однако расположению памяти. команды безусловного условного переходов И ΜΟΓΥΤ изменять ЭТОТ порядок, соответственно безусловно, или при выполнении некоторого условия, задаваемого отношениями типа больше, меньше или равно. В большинстве случаев сравниваются результаты выполнения предыдущей операции и некоторое число, указанное в команде условного перехода. Именно команды условного перехода позволяют строить не только линейные, но также ветвящиеся и циклические программы.

#### 5 Основные характеристики и параметры ЭВМ

Структуру ЭВМ определяет следующая группа характеристик:

- · технические и эксплуатационные характеристики ЭВМ (быстродействие и производительность, показатели надежности, достоверности, точности, емкость оперативной и внешней памяти, габаритные размеры, стоимость технических и программных средств, особенности эксплуатации т.д.);

- · характеристики и состав функциональных модулей базовой конфигурации ЭВМ; возможность расширения состава технических и программных средств; возможность изменения структуры;

- · состав программного обеспечения ЭВМ и сервисных услуг (операционная система или среда, пакеты прикладных программ, средства автоматизации программирования).

#### К основным характеристикам ЭВМ относятся:

Быстродействие это число команд, выполняемых ЭВМ за одну секунду.

Сравнение по быстродействию различных типов ЭВМ, не обеспечивает достоверных оценок. Очень часто вместо характеристики быстродействия используют связанную с ней характеристику производительность.

*Производительность* это объем работ, осуществляемых ЭВМ в единицу времени.

Применяются также относительные характеристики производительности. Фирма Intel для оценки процессоров предложила тест, получивший название индекс iCOMP (Intel Comparative Microprocessor Performance). При его определении учитываются четыре главных аспекта производительности: работа с целыми числами, с плавающей запятой, графикой и видео. Данные имеют 16-и 32-разрядной представление. Каждый из восьми параметров при вычислении участвует со своим весовым коэффициентом, определяемым по усредненному соотношению между этими операциями в реальных задачах. По индексу iCOMP ПМ Pentium 100 имеет значение 810, а Pentium 133-1000.

Емкость запоминающих устройств. Емкость памяти измеряется количеством структурных единиц информации, которое может одновременно находится в памяти. Этот показатель позволяет определить, какой набор программ и данных может быть одновременно размещен в памяти.

Наименьшей структурной единицей информации является **бит**- одна двоичная цифра. Как правило, емкость памяти оценивается в более крупных единицах измерения - байтах (байт равен восьми битам). Следующими единицами измерения служат 1 Кбайт = 210 = 1024 байта, 1 Мбайт = 210 Кбайта = 220 байта, 1 Гбайт = 210 Мбайта = 220 Кбайта = 230 байта.

Емкость оперативной памяти (ОЗУ) и емкость внешней памяти (ВЗУ) характеризуются отдельно. Этот показатель очень важен для определения,

какие программные пакеты и их приложения могут одновременно обрабатываться в машине.

Надежность это способность ЭВМ при определенных условиях выполнять требуемые функции в течение заданного периода времени (стандарт ISO (Международная организация стандартов) 2382/14-78).

Высокая надежность ЭВМ закладывается в процессе ее производства. Применеие сверхбольшие интегральные схемы (СБИС) резко сокращают число используемых интегральных схем, а значит, и число их соединений друг с другом. Модульный принцип построения позволяет легко проверять и контролировать работу всех устройств, проводить диагностику и устранение неисправностей.

*Точность* это возможность различать почти равные значения (стандарт ISO - 2382/2-76).

Точность получения результатов обработки в основном определяется разрядностью ЭВМ, а также используемыми структурными единицами представления информации (байтом, словом, двойным словом).

Достоверность это свойство информации быть правильно воспринятой.

Достоверность характеризуется вероятностью получения безошибочных результатов. Заданный уровень достоверности обеспечивается аппаратурнопрограммными средствами контроля самой ЭВМ. Возможны методы контроля достоверности путем решения эталонных задач и повторных расчетов. В особо ответственных случаях проводятся контрольные решения на других ЭВМ и сравнение результатов.

### Контрольные вопросы:

- 1. Какие элементы входят в состав компьютерных систем?

- 2. Объясните их назначение.

- 3. Как классифицируются ЭВМ в соответствии с используемой формой представления информации при ее преобразовании?

- 4. Поясните структуру ЭВМ,

- 5. Какие устройства входят в архитектуру ЭВМ?

- 6. В чем выражается сущность магистрально-модульного принципа построения ЭВМ?

- 7. Материнские платы.

- 8. Структура чипсетов.

- 9. Перечислите основные характеристики ЭВМ.

### **Тема 2.** Представление информации в ЭВМ. **Арифметические** и логические основы ЭВМ

- 1. Представление информации в ЭВМ. Арифметические и логические основы ЭВМ.

- 2. Основы теории логического проектирования цифровых устройств.

- 3. Базовые элементы ЭВМ, состав и характеристики.

# 1 Представление информации в ЭВМ. Арифметические и логические основы ЭВМ

Внутримашинное представление информации соответствует её отображению в виде цифровых кодов. В результате все действия ЭВМ характеризуются как вычислительные, т.е. такие, которые выполняются в форме прямых операций над числами. Отсюда следует, что одним из основополагающих понятий вычислительной техники является понятие числа.

Числом называется количественная характеристика объекта, отвечающая на вопрос «сколько».

При графическом способе отображения чисел вводится определённая символика в виде системы символов и правил использования этих символов для отображения значений числа. Такая символика позволяет только отображать числа, но не обеспечивает возможностей отображения операций над числами и возможностей определения результатов этих операций. Все эти возможности обеспечиваются системой счисления.

До настоящего времени известны 2 основных способа организации систем счисления. В соответствии с первым способом организуются так называемые символьные системы счисления, а в соответствии со 2-ым способом позиционные системы счисления. И в тех, и в других системах базовым понятием является цифра.

Цифрой называется элементарный символ, используемый для отображения числа. Всякое число отображается как составная конструкция в виде последовательности цифр. В символьной системе счисления каждая цифра имеет одно и то же значение вне зависимости от того, какое место оно занимает в общей записи числа. Примером символьной системы счисления является известная римская система.

В современной практике повсеместно используются позиционные системы счисления. Они характеризуются тем, что цифра в составе записи числа имеет различное значение в зависимости от того, какое место (позицию) оно занимает в общей записи числа.

Например:  $333111=3*10^5+3*10^4+3*10^3+1*10^2+1*10^1+1*10^0$

Различные способы отображения числа предполагают понятия «отображённое число» и «истинное значение числа».

Отображённое число — это есть число, представленное с использованием определённой символики в определённой системе счисления.

Истинное значение числа есть само число как количественная характеристика объекта.

Среди всех позиционных систем истинное значение числа, совпадающее с его отображением, обеспечивает так называемая десятеричная система счисления. Поэтому данная система нашла самое широкое применение и повсеместно используется в обычной практике выполнения вычислительных операций. Во всех других системах счисления запись числа не совпадает с истинным значением числа, в связи с чем, возникает необходимость вычисления истинного значения числа. Кроме того, возникает потребность в выполнении межсистемных преобразованиях чисел, т.е. перевода чисел из одних систем счисления в другие и выполнения эквивалентных операций над числами в различных системах счисления.

Позиционные системы счисления. В позиционной системе число а записывается в виде последовательности цифр, то есть имеет вид:

$$A = a_1 a_2 \dots a_n \cdot a_{n+1} a_{n+2} \dots a_r$$

Здесь группа цифр  $a_1$ - $a_n$  составляет целую часть числа, группа цифр  $a_{n+1}$ - $a_r$  составляют дробную часть числа. Границу записи целой и дробной части определяет десятичная точка (символ). В данной записи каждая цифра в составе числа имеет значение, которое определяется позицией цифры в записи числа. Указанные позиции описываются по порядку влево и вправо от последней цифры целой части числа, которое имеет нулевую позицию. При этом нумерация позиции влево осуществляется с положительным знаком, а вправо с отрицательным знаком. С учётом произведённой нумерации позиции истинное значение числа А определяется как

$$|A| = a_1 p^{n-1} a_2 p^{n-2} \dots a_n p^0, a_{n+1} p^{-1} a_{n+2} p^{-2} \dots a_r p^{-r}$$

где р -основание системы исчисления.

Основанием системы исчисления называется число, которое определяет количество цифр, используемых в данной системе исчисления для отображения произвольных чисел. Указанные цифры образуют базовый цифровой ряд позиционной системы исчисления. В десятеричной системе исчисления базовый цифровой ряд образуют цифры 0,1,2,3,4,5,6,7,8,9. При этом основанием системы исчисления является число10.

В позиционной системе исчисления произвольное число может быть представлено двумя возможными способами:

- а) способ с фиксированной точкой;

- б) способ с плавающей точкой.

Числом a с фиксированной точкой называется такое число а со знаком, которое содержит целую и дробную часть, разделённые символом «десятичная точка». Способ представления числа с фиксированной точкой характеризуется тем, что значение числа размещается на цифровой разрядной сетке установленного формата. Данный формат определяет общую длину разрядной сетки, длину целой и дробной частей, а также положение десятичной точки,

которое фиксируется в отдельном разряде. При этом запись значения числа осуществляется соответственно влево и вправо от десятичной точки. При таком способе представления числа возникают понятия «минимально представимые» значения в заданном формате и максимально представимое значение в заданном формате.

Числом, минимально представимым на заданном формате, называется такое число, которое содержит единицу в младшем дробном разряде, тогда как все остальные разряды заняты нулём.

Максимально представимое число в заданном формате характеризуется тем, что все цифровые разряды разрядной сетки заполнены старшей цифрой базового цифрового ряда используемой системы исчисления.

Всякое число, значение которого меньше минимально представимого, автоматически приравнивается к 0, который в данном случае называется машинным. Всякое число, значение которого превосходит максимально представимое, считается несуществующим и вызывает переполнение разрядной сетки, что является основанием для аварийного прекращения счёта.

Числом А с плавающей точкой называется такое число, запись которого имеет вид:

#### A=MEP

где M — мантисса числа; P — порядок числа; E — признак числа с плавающей точкой.

Например: 1.3987Е2

Мантиссой числа с плавающей точкой называется число со знаком в виде числа с фиксированной точкой, на котором определяется истинное значение числа путём определения положения десятичной точки.

Порядок числа P — это есть число с фиксированной точкой целого типа, которое определяет положение десятичной точки на мантиссе числа при отсчёте на этой мантиссе истинного значения числа.

Истинное значение числа с плавающей точкой определяется как

$$|A| = M*S^p$$

где S – основание системы исчисления.

Таким образом, при использовании формата с плавающей точкой на одной и той же мантиссе может быть воспроизведено бесконечное количество чисел, отличающихся на порядок. Эти числа воспроизводятся путём изменения значения р на единицу, что вызывает эффект точки, плавающей по мантиссе. Диапазон представлений чисел способом с плавающей точкой значительно превосходит диапазон представления чисел способом с фиксированной точкой при использовании одинаковой цифровой разрядной сетки для представления числа.

Представление числа способом с плавающей точкой предполагает обязательное использование мантиссы числа. При этом в общем случае не оговаривается способ организации такой мантиссы, в связи с чем одно и то же число может иметь бесконечное число вариантов записи. С тем, чтобы

исключить элементы неоднозначности представления чисел вводится понятие нормализованной мантиссы.

Нормализованная мантисса - это такая мантисса, которая приведена к виду заранее обусловленного формата. Различают 2 основных формата нормализованных мантисс:

- А) Математически нормализованная мантисса.

- Б) Машинно-нормализованная мантисса.

Математически нормализованная мантисса характеризуется тем, что имеет нулевую целую часть, при этом старший разряд дробной части всегда представлен значащей цифрой. Например, число 375.05, представленное способом с плавающей точкой на математически нормализованной мантиссе, будет иметь вид: 0.37505E3.

Машинно-нормализованная мантисса - имеет целую часть в виде одной значащей цифры. В данном случае число 375.05 будет иметь вид: 3.7505E2.

Примечание: Обычно нормализация мантиссы предполагает определённые нормы обеспечения длины записи мантиссы. Так, представление числовых результатов при компьютерном счёте обычно осуществляется способом с плавающей точкой на машино-нормализованной мантиссе, длина которой определяется моделью ЭВМ и версией ОС.

Двоичная система счисления. Современные средства цифровой вычислительной техники можно отнести к классу технических устройств, в которых реализована двоичная система счисления. Это связано с тем, что представление любого числа в двоичной системе основывается на использовании всего 2-ух цифр: 0 и 1, которые могут быть воспроизведены устройствами простейшей конструкции типа двухпозиционного переключателя.

Двоичная позиционная система счисления характеризуется тем, что её базовый цифровой ряд включает 2 цифры: 0 и 1. При этом основание системы счисления S=2.

Таблица соответствия основных десятиричных чисел двоичным числам

| Дес. система | Дв. система |

|--------------|-------------|

| 0            | 0           |

| 1            | 1           |

| 2            | 10          |

| 3            | 11          |

| 4            | 100         |

| 5            | 101         |

| 6            | 110         |

| 7            | 111         |

| 8            | 1000        |

| 9            | 1001        |

| 10           | 1010        |

| 11           | 1011        |

| 12           | 1100        |

| 13 | 1101    |

|----|---------|

| 14 | 1110    |

| 15 | 1111    |

| 16 | 10000 B |

Арифметика двоичных чисел. Выполнение арифметических операций над двоичными числами выполняется в соответствии со следующими значениями результатов операций:

Двоичное дополнение до двух. Запись всякого числа в любой системе счисления по существу можно расценивать как кодирование числа. Существуют различные способы такого кодирования. В вычислительной технике, в особенности, при работе с двоичными числами широко используется представление числа в виде прямого кода, обратного кода и дополнительного кода.

Прямой код числа характеризуется тем, что число представляется способом с фиксированной точкой. В случае обратного кода — в записи числа цифра 0 заменяется на 1 и наоборот — 1 на 0. Дополнительный код числа образуется путем добавления единицы в младший разряд обратного кода числа.

С использованием дополнительного кода числа можно организовать операцию вычитания чисел в форме операции сложения. Для этого оба числа, участвующие в операции вычитания, преобразуются эквивалентным образом к дробному значению с нулевой целой частью и приводятся к одному формату по длине. Недостающие цифровые разряды в вычитаемом заполняются нулями. Затем для вычитаемого образуется дополнительный код, который складывается с уменьшаемым. Результат операции отсчитывается на тех же цифровых разрядах, что и числа, участвующие в операции. Значение целой части в результате операции отбрасывается. Полученное дробное число преобразуется в исходный формат.

Кодированные вычисления могут производиться с использованием вспомогательных систем счисления, в частности восьмеричной и шестнадцатиричной позиционных систем.

Восьмеричная система исчисления. Перевод чисел из десятеричной системы в двоичную требует выполнения достаточно большого объёма вычислений. Вместе с тем, программирование вычислительной техники на практике требует организации вычислений всех видов только в двоичной системе. Кроме того, адресация памяти ЭВМ также выполняется только в двоичных кодах. Работа с такими кодами, вследствие их большой длины, обычно затруднена для запоминания значений данных. В связи с этим широкое применение находит восьмеричная система исчисления, которая позволяет выполнять двоично-восьмеричные преобразования без промежуточных

вычислений и таким образом облегчает запоминание длинных двоичных кодов. При этом вычислительные операции над двоичными числами могут быть заменены операциями над эквивалентными восьмеричными числами.

Преобразование восьмеричных чисел в двоичные выполняется путём прямого кодирования каждой восьмеричной цифры в составе числа двоичным кодом длиной в три разряда.

Преобразование двоичного числа в восьмеричное выполняется путём разбиения двоичного числа на группы по 3 разряда влево и вправо от десятичной точки с последующим переводом каждого трёхразрядного кода в восьмеричную цифру.

Базовый цифровой ряд восьмеричной системы включает цифры: 0,1,2,3,4,5,6,7. Соответственно, основанием системы исчисления является число 8.

Таблица соответствия между десятеричными и восьмеричными числами

| Дес. сист. | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|------------|---|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|

| Восм.      | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 20 |

| Сист.      |   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |

Преобразование восьмеричного числа в десятеричное выполняется путём вычисления истинного значения восьмеричного числа.

Арифметика восьмеричных чисел. Арифметические операции над восьмеричными числами выполняются также как и над десятичными числами с той лишь разницей, что результат операции оценивается в абсолютных значениях с последующим переводом этих значений в восьмеричный код.

Представление чисел в восьмеричной системе способом с фиксированной и плавающей точкой выполняется по общим правилам для позиционных чисел. Для того, чтобы получить число с фиксированной точкой, достаточно заменить десятичную запятую символом точка. В случае записи числа представленного способом с плавающей точкой, мантисса числа записывается в виде восьмеричного числа, а порядок в виде десятеричного числа.

Шестнадцатеричная система исчисления. В практике программирования ЭВМ использование восьмеричной системы бывает не всегда удобным, В особенности в тех случаях, когда выполняется занесение числовых значений данных в память ЭВМ, поскольку каждый цифровой разряд восьмеричного числа кодируется на трех двоичных разрядах. При занесении такого числа в память ЭВМ его поразрядная длина всегда кратна трем. Поэтому при его размещении в ячейках памяти в виде байтов, длина которых равна восьми двоичным разрядам, происходит потеря незанятых двоичных разрядов, что приводит к нерациональному использованию памяти ЭВМ.

В связи с этим обычно используется шестнадцатеричная система, которая обладает всеми свойствами восьмеричной системы с той разницей, что каждая шестнадцатеричная цифра кодируется на четырех двоичных разрядах. Поэтому при размещении такого числа в памяти ЭВМ в тех случаях, когда его поразрядная длина содержит четное количество цифровых разрядов, оно

занимает целое число байт. И только в случае, когда поразрядная длина числа нечетная, возникают потери 0,5 байт. Таким образом, максимально возможные потери при размещении шестнадцатеричных чисел в памяти не превышают 0,5 байт для каждого числа.

Двоично-шестнадцатиричные преобразования чисел производятся по следующим правилам:

Правило 1. Для того, чтобы преобразовать шестнадцатеричное число в двоичное, следует каждую цифру в составе шестнадцатеричного числа представить в виде двоичного кода на четырех цифровых разрядах.

Правило 2. Для того, чтобы представить двоичное число в виде шестнадцатеричного, его необходимо разбить на группы по 4 двоичных разряда влево и вправо от десятичной точки и каждую группу представить шестнадцатеричной цифрой.

Примечание. Недостающие старшие и младшие разряды двоичного числа дополняются незначащими нулями.

Базовый цифровой ряд шестнадцатеричной системы включает следующие цифры: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F.

Основанием системы является число S=16.

Таблица соответствия десятеричных и шестнадцатеричных чисел.

| Десятирич. сист. | Шестнадцатирич. |  |  |

|------------------|-----------------|--|--|

| деелири і. еист. | сист.           |  |  |

| 0                | 0               |  |  |

| 1                | 1               |  |  |

| 2                | 2               |  |  |

| 3                | 3               |  |  |

| 4                | 4               |  |  |

| 5                | 5               |  |  |

| 6                | 6               |  |  |

| 7                | 7               |  |  |

| 8                | 8               |  |  |

| 9                | 9               |  |  |

| 10               | A               |  |  |

| 11               | В               |  |  |

| 12               | С               |  |  |

| 13               | D               |  |  |

| 14               | Е               |  |  |

| 15               | F               |  |  |

Перевод десятеричных чисел в шестнадцатеричные выполняется по общим правилам межсистемных преобразований для позиционных чисел. Раздельно для целой и дробной части. При записи шестнадцатеричное число помещается индексом Н. В записи числа в крайней левой позиции всегда должна стоять

цифра. Если записываемое число начинается с шестнадцатеричной цифры в буквенном представлении, перед ней следует ставить 0.

Преобразование шестнадцатеричного числа в десятеричное выполняется по правилу вычисления истинного значения позиционного числа.

Сложение и вычитание в дополнительном коде.

При выполнении арифметических операций в современных ЭВМ используется представление положительных чисел в прямом коде (ПК), а отрицательных - в обратном (ОК) или в дополнительном (ДК) кодах. Это можно проиллюстрировать следующей схемой:

| ПК | 0 Мод.дв.числа | 1 | Мод.дв.числа         |

|----|----------------|---|----------------------|

| ОК | 0 Мод.дв.числа | 1 | <u>Мод</u> .дв.числа |

| ДК | 0 Мод.дв.числа | 1 | OK+1 <sub>M3P</sub>  |

|    | a)             |   | б)                   |

Представление чисел в ЭВМ: а) - положительное число; б) - отрицательное число

Общее правило. При алгебраическом сложении двух двоичных чисел, представленных обратным (или дополнительным) кодом, производится арифметическое суммирование этих кодов, включая разряды знаков. При возникновении переноса из разряда знака единица переноса прибавляется к МЗР суммы кодов при использовании ОК и отбрасывается при использовании ДК. В результате получается алгебраическая сумма в обратном (или дополнительном) коде.

Рассмотрим подробнее алгебраическое сложение для случая представления отрицательных чисел в ДК.

При алгебраическом сложении чисел со знаком, результатом также является число со знаком. Суммирование происходит по всем разрядам, включая знаковые, которые при этом рассматриваются как старшие. При возникновении переноса из старшего разряда единица переноса отбрасывается и возможны два варианта результата:

- знаковый разряд равен нулю: результат положительное число в ПК;

- знаковый разряд равен единице: результат отрицательное число в ДК.

Для определения абсолютного значения результата, его необходимо инвертировать, затем прибавить единицу.

Пример:

Вычислить алгебраическую сумму 58 - 23.

$$58_{(10)} o 0011\ 1010_{(2)}$$

- ПК - 28 $_{(10)} o 1001\ 0111_{(2)}$  - ДК Число отрицательное - необходимо перевести в ДК (быстрый перевод)

#### Пример:

Вычислить алгебраическую сумму 26 - 34.

$$26_{(10)} o 0001\ 1010_{(2)}$$

- ПК  $-34_{(10)} o 1010\ 0010_{(2)}$  - ПК  $-1011110_{(2)}$  - ДК  $-1011110_{(2)}$  Быстрый перевод  $-10011010_{(2)}$  Перенос из знакового разряда отсутствует. Число отрицательное в ДК, так как знаковый разряд равен 1.

Вычислим результат, преобразовав его из ДК в ПК:

1111

$$1000_{(2)}$$

(ДК)

1000 0111 Инверсия всех разрядов, кроме знакового

+ 1/1000 1000<sub>(2)</sub> (ПК) = - 8<sub>(10)</sub>

#### Пример:

Вычислить алгебраическую сумму -5 - 1.

$$-5_{(10)}$$

$\rightarrow$  1101 (ПК)  $\rightarrow$ 1011 (ДК)  $-1_{(10)}$   $\rightarrow$  1001 (ПК)  $\rightarrow$ 1111 (ДК)

1011 Перенос из знакового разряда отбросить.

Число отрицательное в ДК, так как знаковый разряд равен 1.

1

$$\leftarrow$$

1010 (2)

Запишем результат, преобразовав его из ДК в ПК:

Признак переполнения разрядной сетки

При алгебраическом суммировании двух чисел, помещающихся в разрядную сетку, может возникнуть переполнение, то есть образуется сумма,

требующая для своего представления на один двоичный разряд больше, чем разрядная сетка слагаемых. Предполагается, что положительные числа представляются в прямом коде, а отрицательные — в дополнительном.

Признаком переполнения является наличие переноса в знаковый разряд суммы при отсутствии переноса из знакового разряда (положительное переполнение) или наличие переноса из знакового разряда суммы при отсутствии переноса в знаковый разряд (отрицательное переполнение).

При положительном переполнении результат операции положительный, а при отрицательном переполнении - отрицательный.

Если и в знаковый, и из знакового разряда суммы есть переносы или этих переносов нет, то переполнение отсутствует.

Рассмотрим простейшие примеры с трехбитовыми словами. Диапазон чисел, которые они представляют, равен от -4 до +3. В рассматриваемых словах 1 бит знака и 2 информационных бита.

1. Алгебраическое суммирование без переноса.

2+1=3

$$010_{(2)}$$

$2_{(10)} \rightarrow 010_{(2)} \Pi K$  +  $001_{(2)}$

$1_{(10)} \rightarrow 001_{(2)} \Pi K$  0  $0 \leftarrow 011_{(2)}$   $0$

Так как перенос в знаковый разряд или из знакового разряда суммы отсутствует, то переполнения нет.

Результат - положительное число в ПК, равное 3.

## 2 Основы теории логического проектирования цифровых устройств

Задачи, решаемые при разработке цифровых логических устройств, можно разделить на две категории:

Синтез - это процесс построения схемы цифрового устройства по заданию.

Анализ - процесс обратный синтезу.

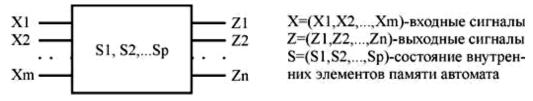

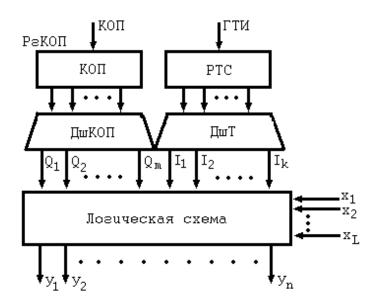

Модель дискретного устройства, отражающая только его свойства по переработке сигналов, называется дискретным (цифровым) автоматом (рисунок 1).

Рисунок 1 – Дискретный цифровой автомат

В общем случае, модель представляет собой многополюсный черный ящик с m входами и n выходами (рис.1). Состояние автомата определяется состояниями сигналов на его входах и выходах. Совокупность входных и

выходных переменных X и Z образуют входное и выходное слово автомата, соответственно.

Различные значения входных переменных образуют алфавит (т.к. алфавит входных и выходных переменных един, в дальнейшем будет рассматриваться только один алфавит). В цифровой технике алфавит входного (выходного) слова содержит два значения (две буквы) "1" и "0".

Каждое слово - набор переменных на входе или на выходе автомата, отличается от другого слова хотя бы одной буквой. Каждая буква слова поставлена в соответствие с номером входа (выхода) автомата.

#### 3 Базовые элементы ЭВМ

Элементами электронных вычислительных машин называются наименьшие функциональные части, на которые можно разделить машину при ее логическом проектировании и технической реализации. Элементы ЭВМ выполняют хранение, преобразование и передачу двоичных переменных, а также ряд вспомогательных функций: задержку сигнала во времени, формирование сигнала с определенными физическими характеристиками и т. п.

Основу элементной базы ЭВМ составляют цифровые интегральные схемы (ИС). Их сложность характеризуется степенью функциональной интеграции  $K_{\mu}$  ( $K_{\mu}$ = lg  $N_{\text{эл}}$  где  $N_{\text{эл}}$  —число элементов И — НЕ либо ИЛИ — НЕ, расположенных на кристалле ИС).

В зависимости от сложности интегральные схемы подразделяются на следующие типы:

МИС — малые интегральные схемы, содержащие один или несколько логических элементов ( $K_u \approx 1$ );

СИС — средние интегральные схемы, содержащие один или несколько функциональных узлов (сумматоров, счетчиков и др.) и имеющие обычно  $K_u = 1...2$ ;

БИС — большие интегральные схемы, содержащие одно или несколько функциональных устройств (арифметическое устройство, арифметикологическое устройство АЛУ, устройство управления УУ, запоминающее устройство ЗУ) и имеющие  $K_{\mu}=2$  - 4;

СБИС — сверхбольшие БИС, выполняющие функции целых цифровых систем (например, микро9BM) и имеющие  $K_u > 4$ .

По типу обрабатываемых сигналов элементы ЭВМ подразделяются на потенциальные, импульсные и импульсно-потенциальные. Длительность потенциального сигнала не ограничена сверху, как правило, кратна длительности такта Т и определяется частотой смены информации.

Длительность импульсного сигнала имеет некоторое постоянное стандартное значение  $t_{\rm u} < T$  и но не зависит от частоты смены информации. Типы сигналов определяют три способа представления (кодирования) информации: потенциальный , импульсный и динамический.

По функциональному назначению элементы делятся на логические, элементы памяти и специальные. К логическим относят элементы,

реализующие функции из базисной системы (базисную функцию). Элементы памяти (триггеры) предназначены для запоминания (храпения) информации, а специальные элементы — для физического преобразования электрических сигналов, т. е. усиления, формирования, генерирования, задержки и т. п.

#### Контрольные вопросы:

- 1. Назначение АЛУ и их виды.

- 2. Структура арифметико-логического устройства.

- 3. Принципы выполнения арифметических операций в ЭВМ над числами с фиксированной запятой.

- 4. Принципы выполнения арифметических операций в ЭВМ над числами с плавающей запятой.

- 5. Объясните принципы арифметики двоично-кодированных чисел.

- 6. Как осуществляется контроль выполнения арифметических операций.

- 7. Задачи, решаемые при разработке цифровых логических устройств.

- 8. Что составляет основу элементной базы ЭВМ?

- 9. Как подразделяются интегральные схемы?

#### Тема 3. Функциональные узлы ЭВМ

- 1. Функциональные узлы ЭВМ.

- 2. Назначение, основные параметры, классификация и принципы построения функциональных узлов ЭВМ.

#### 1 Функциональные узлы ЭВМ

Функциональные узлы ЭВМ представляют отдельные части ЭВМ, реализующие заданные функции в виде определенных машинных операций. Они выполняются, как правило, на основе единых серий элементов ЭВМ. Промышленность выпускает серии элементов (и узлов), на основе которых может быть реализована ЭВМ, выполняющая любые заложенные в нее функции.

Примером подобной серии элементов и узлов может служить комплекс интегральных элементов: К580, КР580, К1810, К1801.

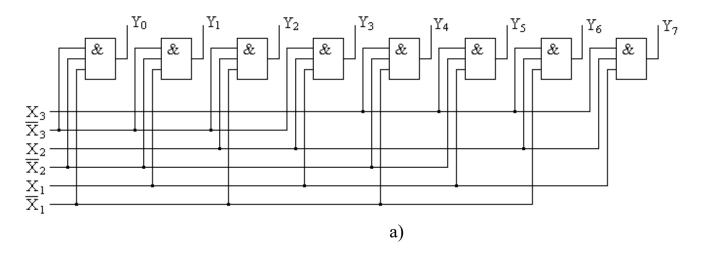

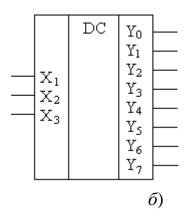

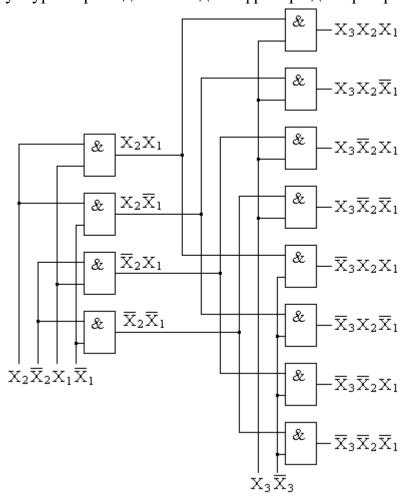

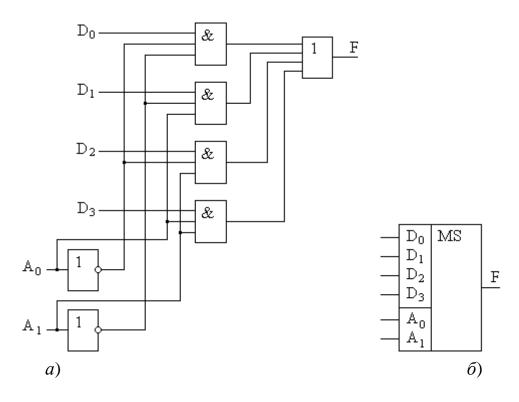

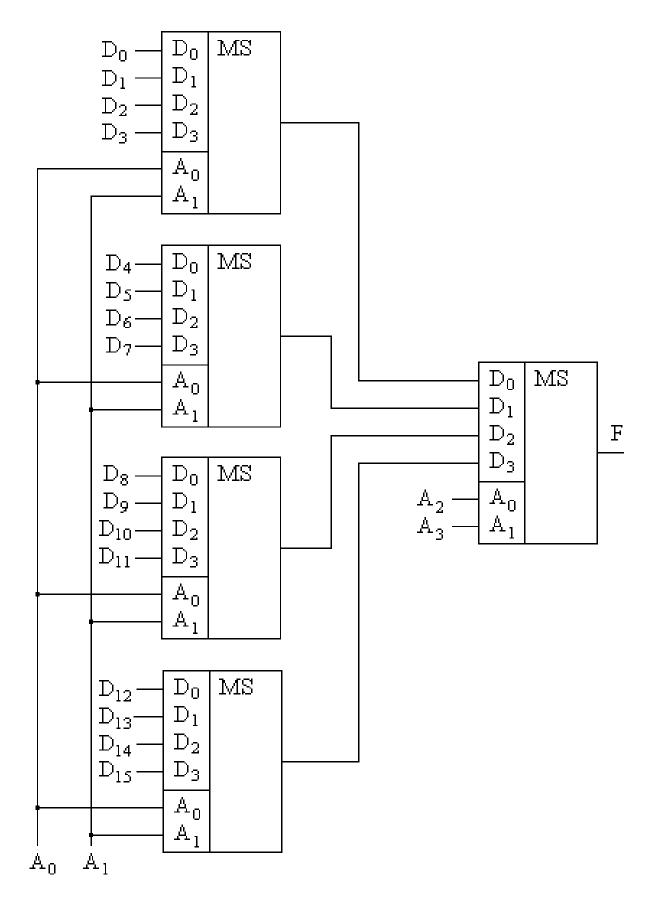

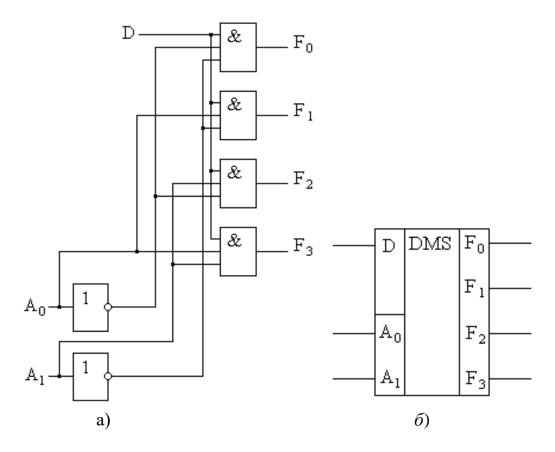

Различают следующие типовые функциональные узлы ЭВМ:

- триггеры;

- регистры;

- счетчики;

- шифраторы;

- дешифраторы;

- мультиплексоры;

- демультиплексоры;

- сдвигатели;

- распределители (уровней и импульсов) и др.

# 2 Назначение, основные параметры, классификация и принципы построения функциональных узлов ЭВМ

<u>Триггер</u> – это функциональный узел ЭВМ, содержащий элемент памяти и схемы управления данным элементом. Существуют различные классификации триггеров, в частности:

- 1. По времени поступления сигналов:

- асинхронные, синхронные.

- однотактные одноступенчатые, двуступенчатые;

- многотактные.

- 2. По базису, т.е. используемым логическим элементам:

- в базисе И–НЕ;

- в базисе ИЛИ-НЕ;

- в смешанном базисе.

- 3. По типу: RS, D, JK, T, DV, DT, RST и др.

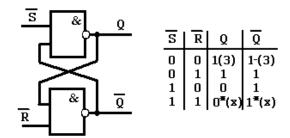

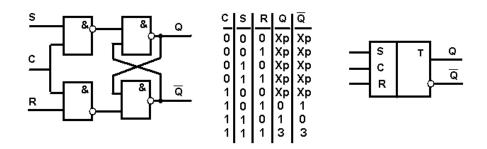

Асинхронные триггеры бывают только RS-типа и представляют логическую схему вида:

Асинхронный RS-триггер в базисе И-НЕ

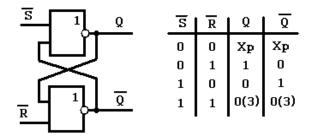

Асинхронный RS-триггер в базисе ИЛИ-НЕ

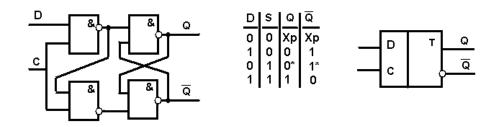

Синхронные триггеры могут быть более разнообразного типа, в частности, следующие:

Синхронные однотактные одноступенчатые триггеры.

Синхронный RS-триггер в базисе И-НЕ

D-триггер в базисе И-HE

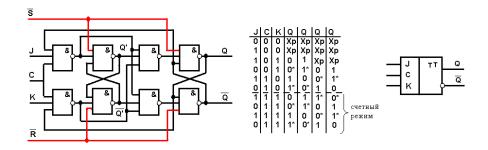

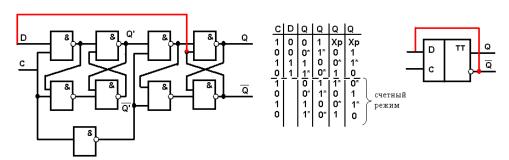

Синхронные однотактные двуступенчатые триггеры.

ЈК-триггер в базисе И-НЕ с запрещающими связями

D-триггер в базисе И-HE с инвертором

Триггеры, имеющие в названии типа букву V — имеют дополнительный синхровход с названием V. Триггеры RST и DvT выполняют комбинированные функции, RST — может выполнять функции RS и T-триггеров, DvT — имеет дополнительный синхровход V, может выполнять функции D и T-триггеров.

**Регистр** — это функциональный узел ЭВМ, предназначенный для записи, хранения, считывания n-разрядного слова информации. Регистры строятся на однотактных или двутактных двуступенчатых триггерах. Они позволяют осуществлять выполнение логических операций, таких как:  $\checkmark, \land, \oplus$ , а также сдвиг информации на заданное количество разрядов.

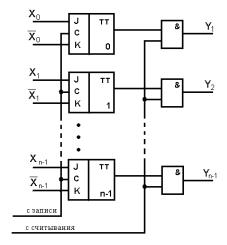

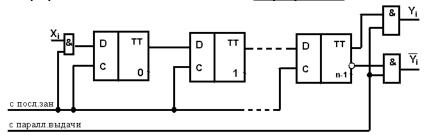

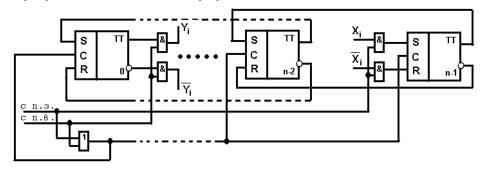

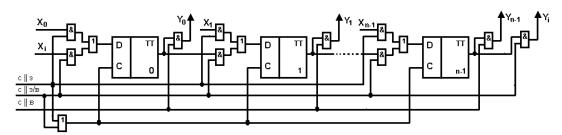

Типы регистров различаются:

- по способу записи-считывания на:

- последовательные т.е. с последовательной записью и считыванием информации;

- параллельные т.е. с параллельной записью и считыванием информации;

- последовательно-параллельные с последовательной записью и параллельным считыванием информации;

- параллельно-последовательные с параллельной записью и последовательным считыванием информации;

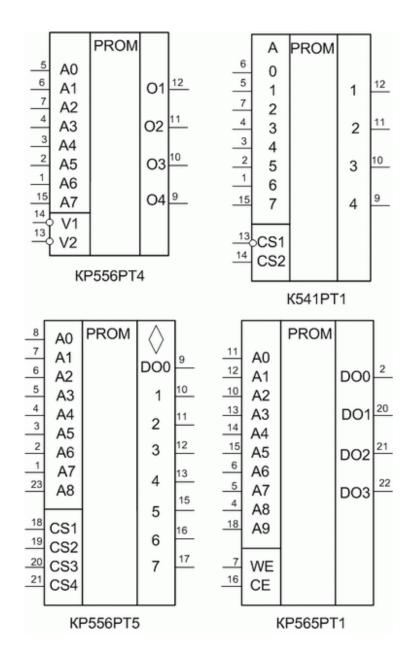

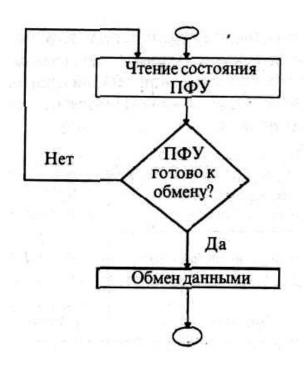

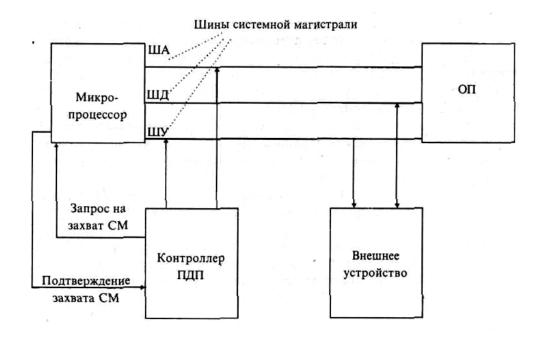

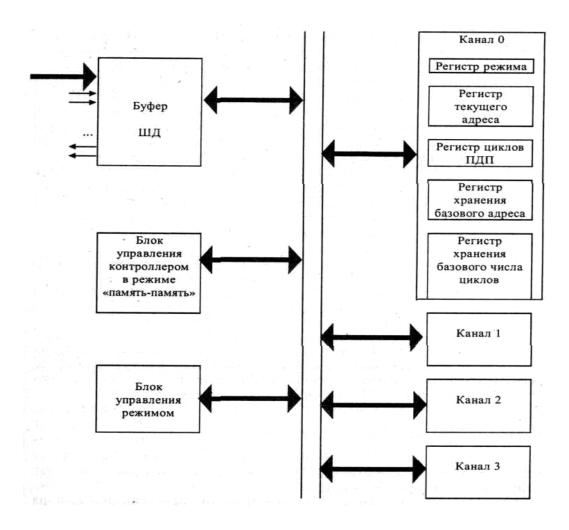

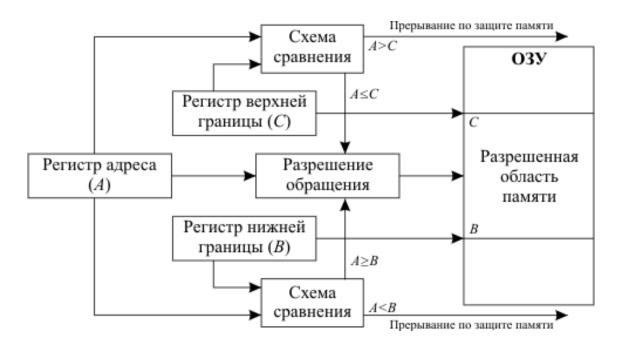

- универсальные с параллельной и последовательной записью и параллельным и последовательным считыванием информации.